| 1  |   |                      |  |

|----|---|----------------------|--|

| 2  |   |                      |  |

| 3  |   |                      |  |

| 4  |   |                      |  |

| 5  |   |                      |  |

| 6  |   |                      |  |

| 7  | D | SI3 Bus Standard     |  |

| 8  |   |                      |  |

| 9  |   | <b>Revision 1.00</b> |  |

| 10 |   |                      |  |

| 11 |   | February 16, 2011    |  |

| 12 |   |                      |  |

| 13 |   |                      |  |

| 14 |   |                      |  |

| 15 |   |                      |  |

| 16 |   |                      |  |

| 17 |   |                      |  |

| 18 |   |                      |  |

| 19 |   |                      |  |

| 20 |   |                      |  |

| 21 |   |                      |  |

| 22 |   |                      |  |

| 23 |   |                      |  |

| 24 |        | <b>Table of Contents</b>                                 |    |

|----|--------|----------------------------------------------------------|----|

| 25 | 1 INT  | RODUCTION                                                | 5  |

| 26 | 1.1 DS | SI3 GENERAL OVERVIEW                                     | 5  |

| 27 | 1.2 DS | SI3 PROTOCOL MAIN FEATURES                               | 5  |

| 28 | 1.2.1  | DSI3 Bandwidth Improvements                              | 5  |

| 29 | 1.2.2  | EMC Improvements                                         | 6  |

| 30 | 1.2.3  | Data Integrity Improvements                              | 6  |

| 31 | 1.2.4  | Cost Controls                                            | 6  |

| 32 | 1.3 US | SE OF THE STANDARD AND LEGAL INFORMATION                 | 6  |

| 33 | 2 DSI3 | BUS TOPOLOGIES, FUNCTIONAL CLASSES AND OPERATIONAL MODES | 7  |

| 34 | 2.1 OV | /ERVIEW                                                  | 7  |

| 35 | 2.2 BU | JS TOPOLOGIES                                            | 8  |

| 36 | 2.2.1  | Point-to-Point Bus Topology                              | 8  |

| 37 | 2.2.2  | Daisy-Chain Bus Topology                                 | 8  |

| 38 | 2.2.3  | Parallel Bus Topology                                    | 9  |

| 39 | 2.3 FU | INCTIONAL CLASSES OF OPERATION                           | 10 |

| 40 | 2.3.1  | Signal Function Class                                    | 10 |

| 41 | 2.3.2  | Power Function Class                                     | 10 |

| 42 | 2.4 Mo | ODES OF OPERATION                                        | 11 |

| 43 | 2.4.1  | Signal Function Class: Command and Response Mode         | 11 |

| 44 | 2.4.2  | Signal Function Class: Periodic Data Collection Mode     | 11 |

| 45 | 2.4.3  | Signal Function Class: Background Diagnostic Mode        | 12 |

| 46 | 2.4.4  | Power Function Class: Command and Response Mode          | 13 |

| 47 | 3 DSI3 | 3 SCALABILITY                                            | 14 |

| 48 | 4 DSI3 | 3 PHYSICAL LAYER                                         | 15 |

| 49 | 4.1 IN | TRODUCTION                                               | 15 |

| 50 | 4.2 FO | DRWARD COMMUNICATION CHANNEL PHYSICAL LAYER              | 15 |

| 51 | 4.2.1  | Forward Channel Physical Layer - Master Perspective      | 16 |

| 52 | 4.2.2  | Forward Channel Physical Layer - Slave Perspective       | 17 |

| 53 | 4.2.3  | Forward Communication Channel Data Bit Encoding          | 18 |

| 54 | 4.2.4  | Forward Communication Channel Timing                                   |    |

|----|--------|------------------------------------------------------------------------|----|

| 55 | 4.3 RH | EVERSE COMMUNICATION CHANNEL PHYSICAL LAYER                            |    |

| 56 | 4.3.1  | Reverse Communication Channel Physical Layer - Slave Perspective       |    |

| 57 | 4.3.2  | Reverse Communication Channel Physical Layer - Master Perspective      | 20 |

| 58 | 4.3.3  | Reverse Communication Channel Data Bit Encoding                        | 21 |

| 59 | 4.4 RE | EVERSE COMMUNICATION CHANNEL TIMING CONSIDERATIONS                     |    |

| 60 | 4.5 SY | STEM TIMING CONSIDERATIONS                                             |    |

| 61 | 4.6 NU | JMBER OF DSI BUSES AND NODES                                           |    |

| 62 | 4.7 CI | ASS-MIX AND MODE RESTRICTIONS AND NUMBER OF NODES                      |    |

| 63 | 5 DSI3 | 3 DATA LINK LAYER                                                      | 26 |

| 64 | 5.1 IN | TRODUCTION                                                             |    |

| 65 | 5.1.1  | Command Message Bit Order                                              |    |

| 66 | 5.1.2  | Response Message Bit Order                                             |    |

| 67 | 5.2 SI | GNAL FUNCTION CLASS                                                    | 27 |

| 68 | 5.2.1  | Command and Response Mode Packet Formats                               | 27 |

| 69 | 5.2.2  | Periodic Data Collection Mode Packet Formats                           |    |

| 70 | 5.2.3  | Background Diagnostic Mode Packet Formats                              |    |

| 71 | 5.3 PC | OWER FUNCTION CLASS TRANSACTIONS                                       |    |

| 72 | 5.4 EF | ROR CHECKING                                                           |    |

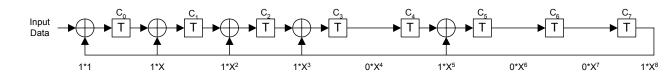

| 73 | 5.4.1  | Command and Response Mode CRC                                          |    |

| 74 | 5.4.2  | Periodic Data Collection Mode CRC                                      |    |

| 75 | 5.4.3  | Background Diagnostic Mode CRC                                         |    |

| 76 | 6 DSI3 | 3 ADDRESSING                                                           |    |

| 77 | 6.1 IN | TRODUCTION                                                             |    |

| 78 | 6.2 PH | IYSICAL ADDRESSING FOR SLAVES                                          |    |

| 79 | 6.3 AI | DDRESS ASSIGNMENT METHODS                                              |    |

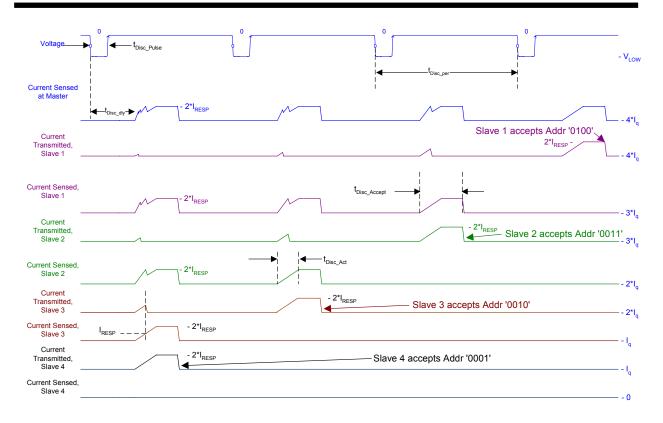

| 80 | 6.3.1  | Address Assignment Method for Parallel Connected Slaves                |    |

| 81 | 6.3.2  | Address Assignment Method for Bus Switch Connected Daisy Chain Devices |    |

| 82 | 6.3.3  | Address Assignment Method for Resistor Connected Daisy Chain Devices   | 40 |

| 83 | 7 SLA  | VE MEMORY MAP                                                          | 42 |

| 84 |        | EOUIRED SLAVE REGISTERS                                                |    |

| 85 | 7.1.1  | ICTYPEID Register | 43 |

|----|--------|-------------------|----|

| 86 | 7.1.2  | ICMFGID Register  | 43 |

| 87 | 7.1.3  | ICREV Register    | 43 |

| 88 | 7.1.4  | MODTYPE Registers | 44 |

| 89 | 7.1.5  | MODMFGID Register | 44 |

| 90 | 7.1.6  | MODREV Register   | 44 |

| 91 | 7.1.7  | DSIREV Register   | 44 |

| 92 | 7.1.8  | PHYSADDR Register | 45 |

| 93 | 7.2 RE | QUIRED SLAVE DATA | 45 |

|    |        |                   |    |

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

#### 94

# **1 INTRODUCTION**

## 95 **1.1 DSI3 General Overview**

96 This document defines the 3rd generation Distributed System Interface (DSI3). It documents the bus topologies,

operational modes and functional classes of DSI3 bus systems and the associated electrical and physical characteristics.

It also defines the message protocol, message transaction models, message formats, bit transmission order and message

99 error checking.

100 DSI3 is a third generation satellite interface bus primarily intended for safety critical communication between a central

- 101 master interface and multiple satellite nodes, also called slaves. Slave nodes can be implemented as simple state 102 machines or as microprocessor or DSP based controllers. The slaves can provide raw data signal sources or pre-

- processed signal sources. Each slave can contain a single data source or multiple data sources. Slave nodes can also

- 104 provide output and control functions.

- 105 Included within the DSI3 protocol is a Discovery Mode whereby slave devices automatically determine their position

- 106 on a serial daisy-chain bus and each slave is assigned a unique physical address. The Discovery Mode allows for the

- 107 identification of slaves with identical features and part number according to their position on the serial daisy-chain bus.

108 For slaves with unique characteristics, the Discovery Mode can be used to ensure that the device with the correct

109 capability is in the proper location of the serial daisy-chain bus.

110 DSI3 includes a fail silent philosophy and an optional Background Diagnostic Mode that operates during normal

- 111 periodic sampling mode. The Background Diagnostic Mode provides advanced services for diagnostics and functional

- 112 safety. The fail silent philosophy is enhanced by Background Diagnostic Mode.

- 113 The primary target application area for the DSI3 network is automotive airbag systems however it is anticipated that the 114 new features of the protocol will allow the use of DSI3 in other application areas.

## 115 **1.2 DSI3 Protocol Main Features**

116 The fundamental strengths of previous DSI versions remain and new elements have been adopted where necessary to

- 117 meet the expanded goals of an improved bus standard. Lessons learned from previous DSI versions, competing

- strategies and the expectations of users have been considered in the development of DSI3.

- 119 DSI3 provides an efficient bi-directional communication scheme by means of forward and reverse channels. The

- 120 forward communication channel defines master to slave communication and the reverse communication channel

- 121 defines slave to master communication. The forward and reverse communication channels operate at half-duplex in

- 122 contrast to previous versions of the protocol. Several modes of operation are provided to optimize performance of both

- the forward and reverse communication channels to match the needs of the application. All modes are synchronous

- since all transactions are initiated by the master.

- 125 The DSI3 protocol has been designed to improve upon the capabilities of all existing sensor bus protocols. In

- 126 particular there are bandwidth improvements, EMC improvements and data integrity improvements. There are also 127 fundamental changes that allow for reduced cost implementations.

## 128 **1.2.1 DSI3 Bandwidth Improvements**

- 129 Bandwidth improvements are the result of an efficient Time-Division-Multiple-Access (TDMA) method utilizing

- multi-level source coding of the response signal, a global clock management scheme, an optimized reverse channel

strategy and an increased bit-rate.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 132 **1.2.2 EMC Improvements**

133 DSI3 includes fundamental changes designed to improve electromagnetic compatibility. EMC improvements are

achieved by reducing the master induced voltage fluctuations on the bus. For DSI3 the reduction in the number of

135 master induced voltage fluctuations occurs as a result of a preconfigured periodic response stream. The fundamental

frequency of the master induced voltage fluctuations has been reduced by nearly two orders of magnitude (from

137 200kHz to approximately 4kHz) compared with previous versions of DSI, resulting in further significant AM band

138 emissions reductions.

## 1391.2.3Data Integrity Improvements

140 The DSI3 Protocol has features designed to address the requirements of safety critical communications. In particular 141 there are mechanisms built in to improve the safety case of the protocol. Examples of the mechanisms include: source 142 identification, Background Diagnostic Mode, keep alive counters, and increased error detection capability.

## 143 **1.2.4 Cost Controls**

The DSI3 Protocol adopts a philosophy that allows system and device implementers to scale the protocol to meet the specific requirements of an application. The protocol can be scaled in several dimensions whereby a base functionality is extended with additional features to meet more demanding or varied applications.

## 147 **1.3 Use of the standard and Legal Information**

148 This specification was developed within the DSI Consortium ("DSI"). Use of this specification is voluntary and is 149 subject to the DSI Consortium Bylaws and Membership Agreement.

150 This specification is supplied "AS IS." DSI Disclaims liability for any personal injury, property, or other damage, of

151 any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from

the publication, use of, or reliance upon this, or any other DSI document. DSI makes no warranties or representations

as to the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty,

154 including any implied warranty of merchantability or fitness for a specific purpose, or that the use of the material

155 contained herein is free from patent infringement.

# **2 DSI3 Bus Topologies, Functional Classes and Operational Modes**

## 157 **2.1 Overview**

The DSI3 protocol manages the formation of networks consisting of a *master* node and one or more *slave* nodes. A system can consist of one or more master nodes. Communication between the master and slaves follows a command and response transaction model with a separate *command phase* and *response phase*. The interconnection of a master node and one or more slave nodes is defined by a bus topology. The DSI3 protocol defines point-to-point, serial daisychain and parallel bus topologies.

163 The DSI3 protocol defines two functional classes of bus operation: the Signal Function Class and the Power Function Class. The Signal Function Class is optimized for periodic data collection from data sources. Signal Function Class 164 165 slaves can also provide outputs to control logic level functions within the limits and restrictions placed on quiescent current of the Signal Function Class. The Power Function Class is optimized to support power outputs but also 166 supports data sources. The Power Function Class utilizes an additional power-phase to supply bus power to the output 167 loads. For the Power Function Class, current draw restrictions place limits on when current is allowed to flow into the 168 169 loads. Generally the Signal Function Class and the Power Function Class must maintain a constant quiescent current 170 draw during at least the response phase but typically for both the command and response phases. In the context of this 171 specification Power Function Class implies that a slave controls a load and isolates the response communication current 172 draw from the master supplied load current delivered into a power output. 173 The DSI3 protocol provides several modes of operation. These are broadly divided into a Command and Response

Mode and a Periodic Data Collection Mode. For Signal Function Class devices, the Command and Response Mode is utilized to start and configure the bus and thereby form the network. For an application that requires immediate functionality at power-on, a pre-programmed configuration can be loaded into non volatile slave memory. In this case the necessary bus configuration and network formation is available immediately after bus start-up. The Periodic Data

178 Collection Mode is entered after bus initialization, configuration and network formation. The Periodic Data Collection

179 Mode also defines an optional Background Diagnostic Mode for low speed diagnostics that occurs without interrupting

180 the periodic data collection.

181 For Power Function Class devices, the Command and Response Mode is used to control and monitor outputs and data

182 sources. The Periodic Data Collection Mode is not intended for the Power Function Class.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 184 **2.2 Bus Topologies**

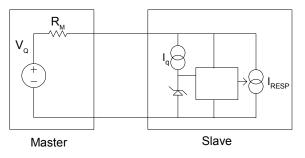

## 185 2.2.1 Point-to-Point Bus Topology

186 The point to point topology consists of a single master node and a single slave node. For the Signal Function Class the

187 slave node can contain a single data source or multiple data sources. For the Power Function Class the slave node

188 provides output signals and optionally data sources. The wiring between the master and the slave are typically twisted 189 pairs and supply both communication signals and the quiescent current for basic slave internal operation. For Power

190 Function Class devices, power is delivered through an additional power phase.

191

192

## Figure 2-1: Point to Point Topology

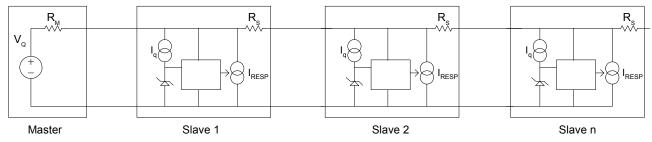

## 193 2.2.2 Daisy-Chain Bus Topology

194 The fundamental application for the daisy-chain topology is to determine relative position within a series

interconnection of potentially identical slaves. This can be accomplished with either a series sense resistor or a seriesbus switch.

197 If series sense resistors are used, the Discovery Mode determines a slave's relative position in the serial daisy-chain and

198 manages address assignment during network formation. Typically slaves on a daisy-chain bus are assigned a physical 199 address at the time of network formation after bus power-up. Alternately the slaves can be pre-programmed with a

address at the time of network formation after bus power-up. Alternately the slaves can be pre-programm physical address and verified via Discovery Mode.

201 202

Figure 2-2: Daisy Chain Topology with Sense Resistors

The serial daisy-chain can implement a bus switch in lieu of or in addition to the sense resistor. The use of a bus switch allows isolation of faulted portions of the bus in applications that require fault isolation. A bus switch allows connection of separate bus segments connected via the bus switch. The Discovery Mode acts on (discovers) individual segments and each segment is discovered separately. When a bus switch is encountered at the end of a bus segment, the master commands the slave to close the bus switch to connect the additional slaves to the bus. The new slaves are discovered as each additional bus segment is connected. The master has a priori knowledge of the bus switches and therefore the segmented bus architecture. The Discovery Mode is described later in this specification.

210

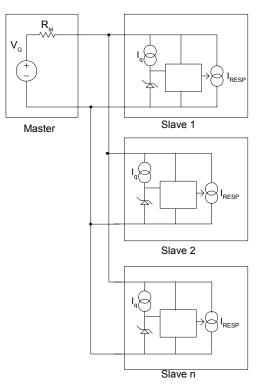

## 211 2.2.3 Parallel Bus Topology

The parallel bus topology requires pre-programmed physical addresses. The main application for the parallel bus is to limit the voltage drops along the bus and allow for more slave nodes on the bus.

214

215

Figure 2-3: Parallel Bus Topology

216 The parallel connections can be implemented at the master side, the slave side or in the wire harness. When

217 implemented in the master side the master must provide the connection pins required for the required number of slaves

and make the pass thru trace connections. When implemented on the slave side the slave must provide the necessary

interconnection pins and the pass thru trace connections. When implemented in the harness the parallel connections are typically splices.

221 The decision of where to make the parallel connections is an implementation choice and can impact the total system

- level costs. The DSI3 protocol allows complete freedom of choice in the connection strategy of the parallel

- connections.

The parallel connected slaves may include a bus switch. In this case the bus switches can connect new bus segments. These new bus segments are discovered as described above for additional segments within a serial daisy-chain.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 227 **2.3 Functional Classes of Operation**

## 228 2.3.1 Signal Function Class

The Signal Function Class is optimized for applications that prioritize high speed periodic data collection. Signal Function Class slaves can implement single or multiple data sources at each slave node. The Signal Function Class can utilize either the Command and Response Mode or the Periodic Data Collection Mode or a combination of both modes. For example a pre-configured parallel connected network could transition immediately into the Periodic Data Collection Mode. Whereas a serially connected daisy-chain bus would use the Command and Response Mode along with the Discovery Mode to form and configure the network and then transition into the Periodic Data Collection Mode.

As mentioned in section 2.1 there are restrictions on Signal Function Class quiescent current levels. The fundamental restriction is that the quiescent current must remain relatively constant during the response phase within the limits specified in Section 4.3. For Signal Function Class slaves the power supply is generally designed to draw constant quiescent current for both the command and response phase as well as manage inrush current, energy extraction and energy storage for micro-break backup purposes.

## 241 **2.3.2 Power Function Class**

242 The Power Function Class is optimized for applications with control functions that require power and current levels

that cannot be supported by the Signal Function Class. The Power Function Class utilizes the command phase and the

response phase with the addition of a power phase. The Power Function Class controls output loads by coordinating the state of output signals during the command phase, the response phase and the power phase. Power Function Class

slaves can implement single or multiple output sources. Power Function Class slaves require an energy extraction

247 mechanism that provides isolation between the power phase and the command and response phases.

For Power Function Class slaves the same fundamental restriction for Signal Function Class slaves applies: the

249 quiescent current must remain relatively constant (or essentially zero) during the response phase, within the limits

specified Section 4.3. During the power phase the Power Function Class must provide isolation between the voltage

level associated with the power phase and the voltage levels during the command and response phases.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 253 **2.4 Modes of Operation**

## 254 **2.4.1** Signal Function Class: Command and Response Mode

The Command and Response Mode (CRM) is used for network formation and bus configuration for Signal Function Classes. The Command and Response Mode provides services that allow for the reading of and writing to slave memory and changing the internal state of the slave. The Command and Response Mode format is defined in Section 5

258 of this specification.

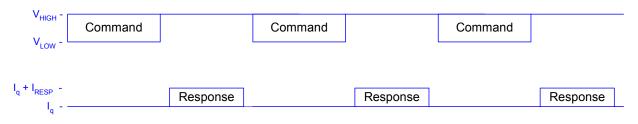

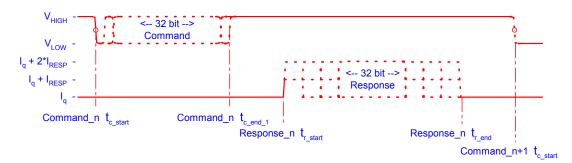

259 The following figure represents the Command and Response Mode timing philosophy for the Signal Function Class.

260 The command signals are Manchester encoded voltage levels defined as  $V_{HIGH}$  and  $V_{LOW}$ . The response signals are

261 multi-level source encoded currents modulated on top of the total slave quiescent current that is present during the

response phase. The command and response timings, voltages, currents and encodings are described in Section 4 of

this specification.

## Figure 2-4: Signal Function Class - Command and Response Mode

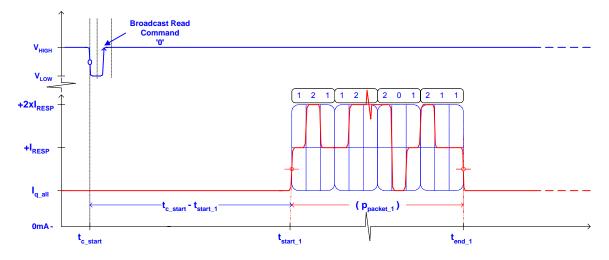

## 266 **2.4.2 Signal Function Class: Periodic Data Collection Mode**

The Periodic Data Collection Mode (PDCM) is optimized for applications that require high speed synchronous data collection. In the context of this specification synchronous data collection means that the data samples are synchronized by the master through synchronization events. The actual data samples are therefore synchronous with the master synchronization event however the data samples may or may not be simultaneous. The distinction between simultaneous sampling and synchronous sampling is addressed by the implementation and is not controlled by this specification. This allows the system implementer to either choose simultaneous sampling or prioritize the relative latency of the data sources.

The following figure represents the command and response timing philosophy for the Periodic Data Collection Mode.

The command transmitted by the master can be either a single bit Broadcast Read Command or a Background

Diagnostic Mode command. The commands are Manchester encoded using the same voltage levels defined for the

commands used during the Command and Response Mode. The response signals are multi-level source encoded

currents assembled into packets modulated on top of the total slave quiescent current. Furthermore the response

279 packets from multiple data sources are time multiplexed utilizing a TDMA approach and separated by inter-packet

separations. The command and response timings, inter packet separation timings, voltages, currents and encodings are

- further described in Sections 4 and 5 of this specification.

- For the Periodic Data Collection Mode the protocol requires that the master node be synchronized with the ECU's clock and must meet the timing requirements as defined in Section 4 of this specification.

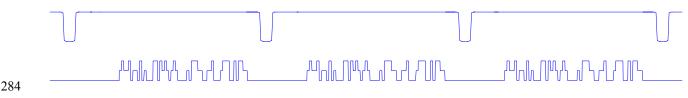

#### Figure 2-5: Signal Function Class - Periodic Data Collection Mode

## 286 **2.4.3** Signal Function Class: Background Diagnostic Mode

An optional low speed diagnostic communication channel called Background Diagnostic Mode (BDM) is defined 287 288 within the DSI3 specification. The Background Diagnostic Mode does not interfere with the Periodic Data Collection 289 Mode; however the system implementer must reserve some bandwidth for the Background Diagnostic Mode. The 290 reserved bandwidth always starts at the beginning of the sample period. The percentage of the sample period reserved 291 can be adjusted to meet the needs of the application. The forward and reverse data packets are split into sequential 292 parts that are transmitted during consecutive periods – first the command bits and then the response bits. The reserved 293 bandwidth is shared between the low speed forward channel and the corresponding low speed reverse channel. The 294 Background Diagnostic Mode provides services for data integrity functionality and uses a different response format and 295 error detection format. This prevents the classic masquerade phenomena that could lead to misinterpretation of data.

```

296

```

#### 297 **F**

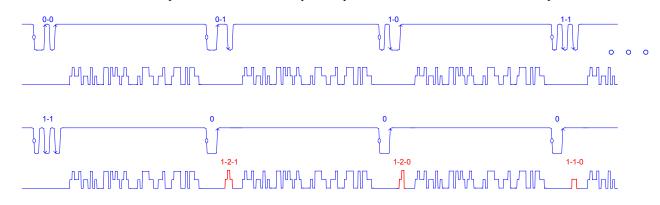

## Figure 2-6: Signal Function Class - Background Diagnostics Mode Command and Response Bits

Figure 2-6 shows a portion of a command sequence along with the normal periodic responses and a Background Diagnostic Mode response. In the example shown in Figure 2-6 there are two command bits sent every period (0-0, 0-1, 1-0 and 1-1). The command (complete command not shown) is followed by the response. The first three response symbols are shown (1-2-1, 1-2-0, and 1-1-0). As in Periodic Data Collection Mode, each of the response symbols is a coded representation of a corresponding 4-bit data nibble. The format for the command and response messages is covered in Section 5.2.3.

The bit-rate of the Background Diagnostic Mode is determined by the number of forward and reverse channel bits that can be transmitted in the time reserved. An example Background Diagnostic Mode configuration may use the following:

- 10% of a 250uS sample period reserved for Background Diagnostic Mode

- A reverse chip time of 3 us. The forward bit time is fixed at 8 us.

309 With this configuration, 2 command bits or 4 response bits can be sent every 250uS. This results in a Background

Diagnostic Mode with an 8kbps forward bit-rate and a 16kbps reverse bit-rate. One 32-bit diagnostic command and one 310 32-bit diagnostic response can occur in every 6mS period of time.

312 Complex transactions are also possible whereby multiple slaves respond in successive sample intervals in the case of a

- 313 broadcast diagnostic request. In the case of a broadcast command, once the command is transmitted, the slaves transmit

- their complete response in sequential order based on their source identification, starting from Source ID = 1.

- 315

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

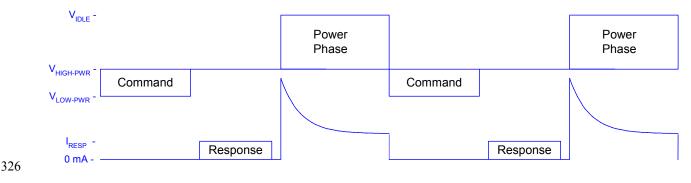

## 316 **2.4.4** Power Function Class: Command and Response Mode

317 The Command and Response Mode is used for network formation, bus configuration and actuator controls for the Power Function Class. The following figure represents the Command and Response Mode timing philosophy for the 318 Power Function Class. The Power Function Class uses the same command phase and response phase formats as the 319 320 Signal Function Class. The command signals are Manchester encoded voltage levels defined as  $V_{HIGH-PWR}$  and  $V_{LOW-}$ 321  $_{PWR}$ . The power phase is implemented as an additional bus level defined as  $V_{IDLE}$ . The response signals are multi-level source encoded currents. The response current signals are required to be isolated from the slave load current. The 322 required isolation of response current from load current is a consequence of the energy extraction used for the Power 323 Function Class. The command and response timings, voltages, currents and encodings are described in Section 4 of 324 325 this specification.

Figure 2-7: Power Function Class - Command and Response Mode

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

#### 328

349 350

351

# 3 DSI3 Scalability

329 The DSI3 protocol is scalable in several dimensions. In addition to choosing the functional classes and modes of 330 operation, the device and system implementers can scale additional elements of the DSI3 protocol to meet the system 331 requirements. Typically the protocol is scaled according to the target function class and the overall required performance of the system. As the performance goals are expanded, elements of the protocol can added or scaled to 332 333 meet new requirements. The scalability allows optimization of cost versus performance. Within the context of the 334 protocol scalability the resultant system performance is based on the lowest common capability in a *controlling* 335 dimension. DSI3 systems may accommodate slaves with lower levels of performance in some of the scalable 336 dimensions. Scalable dimensions include the following:

- The minimum and maximum operating voltages can be defined by the system implementers within the limits

specified in Section 4.2. The minimum and maximum voltage capability of the resulting system is derived

from the least capable device on the bus.

- The number of slaves in a system is based on the supply current capability and current limit of the master device and can be defined by the system implementer within the limits specified in Section 4.2.1 and Section 4.3.1. The system must be designed such that it does not exceed the ratings of the least capable device on the bus. Slaves designed with a lower fault current capability could be damaged if used in a system that could supply higher fault current.

- The sample rate of the system can be defined by the system implementers. The sample rate is a function of the forward and reverse channel bit rates and the number of bits required in the sample interval. The number of bits required in the sample interval is based on the data precision required, the number of data sources and the required safety-case capability.

- 4. The reverse communication channel bit rate can be defined by the system implementers within the limits specified in Section 4.3. The overall system reverse communication channel bit rate must fall within the capability of every device in the system.

- 5. The Data Link Layer can be defined by the system implementers within the limit specified in Section 5. The Data Link Layer can be hard-coded at either the master or the slaves. If the Data Link Layer is hard-coded at the master then all devices must support the same Data Link Layer. If the master supports a configurable Data Link Layer, then slaves with different Data Link Layers can be supported in any combination within the capability of the system.

- 6. Clock synchronization and timing optimization occurs at multiple levels and is considered a shared

responsibility among the devices in the system. Simple low speed system goals can be met with minimal clock

synchronization and no timing optimization. More complex high speed system goals can be met by utilizing

the temporal framework to optimize system timing, as described in Section 4.5. Devices of minimal capability

can be mixed with more capable devices on a bus however the system implementers must configure the timing

to account for the mix of capabilities. The theoretical maximum system capability will be compromised by the

less capable devices.

- 364

7. System fault tolerance and operability can be defined by the system implementers through both physical layer configurations and Data Link Layer configurations. Fault detection and operability is a shared responsibility between the master and slave(s). If desired, fault isolation can be implemented at the slaves through the use of bus switches.

- Parameters in this document marked with a "1" are scalable parameters. Scalable parameters include a controlling

dimension number from the above list as well as a parenthetic suggested value for typical systems.

- 370 The scalable parameter capability of devices in a system must be documented in the device datasheets to allow the

- 371 system implementer to determine the lowest common capability in each controlling dimension.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

372

# 4 DSI3 Physical layer

## 373 4.1 Introduction

DSI3 defines a forward channel for master to slave communication and a reverse channel for slave to master

communication. The forward channel uses voltage fluctuations and the reverse channel uses current fluctuations. DSI3

uses a half-duplex command and response transaction model. With the command and response transaction model the

master always initiates the communication cycle via a command.

The physical layer consists of a connection between a single master and one or multiple slaves. The physical layer interface provides both power and data communication signals. The bus topologies are defined in section 2.2.

The command and response transactions occur in sequence. The half-duplex command and response characteristic is shown in section 2.4 for both the Signal Function Class (Figure 2-4) and for the Power Function Class (Figure 2-7).

For the Periodic Data Collection Mode (Figure 2-5 and Figure 2-6), one or more slaves encode their data source(s)

383 utilizing an optimized multi-level source coded TDMA method. The source coding encodes data nibbles into multi-

level symbols. System timing optimizations are also possible through the use of the global clock synchronization, clock

385 management and innovative response time assignment methods. These system timing optimizations are covered in 386 Section 4.5.

## **4.2 Forward Communication Channel Physical Layer**

388 Two modes of communication are defined. The Command and Response Mode is used for system configuration and

for applications that require significant message traffic in both the forward and reverse directions. The Periodic Data

390 Collection Mode is used for applications that require significant message traffic in only the reverse direction. The

Background Diagnostic Mode allows for low speed bidirectional message traffic while preserving most of the

bandwidth for high speed periodic data collection (reference Section 2.4.3).

393 The forward communication channel physical layer maximum ratings are listed in Table 4-1

| Item | Characteristic / Symbol    | Condition / Notes     | Max                        | Unit |

|------|----------------------------|-----------------------|----------------------------|------|

| 1.   | V <sub>IDLE</sub>          | Power Function Class  | 25                         | V    |

| 2.   | V <sub>HIGH</sub>          | Signal Function Class | 20                         | V    |

| 3.   | Reverse Voltage Protection | Power Function Class  | $12 (-I_{CL_PWR_MAX})$     | mA   |

| 4.   | Reverse Voltage Protection | Signal Function Class | $12 (-I_{CL_{SIG_{MAX}}})$ | mA   |

394

## Table 4-1: Forward Communication Physical Layer Maximum Ratings

395

## 3964.2.1Forward Channel Physical Layer - Master Perspective

### 397 4.2.1.1 Signal Function Class Forward Channel Physical Layer – Master Perspective

398 The  $V_{HIGH}$  and  $V_{LOW}$  voltages are required for all operational modes of the Signal Function Class.

The average value of the  $V_{HIGH}$  voltage is held constant and the  $V_{LOW}$  voltage is produced relative to  $V_{HIGH}$  such that V<sub>HIGH</sub> minus  $V_{LOW}$  is equivalent to  $V_{DELTA}$ . For typical applications the master derives the  $V_{HIGH}$  and  $V_{LOW}$  voltages from an externally regulated voltage source with sufficient voltage and current capabilities.

402 The master is responsible for supplying power to the bus loads. The total bus load consists of static and dynamic loads. 403 The static loads are the slave quiescent currents. The dynamic loads consist of the response currents and the bus

405 The state loads are the stave quiescent currents. The dynamic loads consist of the response currents and the bus 404 currents required to charge and discharge the harness and load capacitors used for bus filtering and stabilization. The

slave quiescent current is typically supplied by the master at either of the  $V_{\text{HIGH}}$  or  $V_{\text{LOW}}$  voltages. As an alternative for

406 extreme low voltage applications the Signal Function Class slave could supply quiescent current from a backup 407 capacitor while at the  $V_{LOW}$  voltage.

| Item | Characteristic / Symbol                                                                           | Condition / Notes                                                         | Min              | Тур | Max              | Unit |

|------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|-----|------------------|------|

| 5.   | V <sub>HIGH</sub>                                                                                 | Signal High Voltage                                                       | <b>1</b> (3)     |     | 20               | V    |

| 6.   | V <sub>HIGH_P</sub> -p drift                                                                      | Variation in V <sub>HIGH</sub> Over 10ms Ignoring<br>Effects of Signaling | -150             |     | 150              | mV   |

| 7.   | R <sub>M</sub>                                                                                    | Master Source Resistance                                                  |                  |     | 10               | Ω    |

| 8.   | V <sub>HIGH_P-P</sub> During Response Phase                                                       | Measured at Master,<br>Peak to Peak Response Current ≤27mA                | -500             |     | 500              | mV   |

| 9.   | I <sub>CL_SIG_MAX</sub>                                                                           | Supply Voltage Current Limit,<br>Measured at Master                       | <u>‡</u> 2 (80)  |     | <b>‡</b> 2 (100) | mA   |

| 10.  | $V_{\text{HIGH}}$ Minus $V_{\text{LOW}}$<br>Differential Signaling Voltage ( $V_{\text{DELTA}}$ ) | Measured at Master, $I_Q \leq 40 \text{mA}$                               | 1.75             | 2   | 2.25             | V    |

| 11.  | $V_{\text{HIGH}}$ to $V_{\text{LOW}}$ Slew Time                                                   | $C_{BUS} = 15 nF$ , 90% to 10% of $V_{DELTA}$                             | <b>1</b> 2 (333) |     | 1000             | ns   |

| 12.  | $V_{\text{LOW}}$ to $V_{\text{HIGH}}$ Slew Time                                                   | $C_{BUS} = 15 nF$ , 10% to 90% of $V_{DELTA}$                             | <b>1</b> (333)   |     | 1000             | ns   |

408

Table 4-2: Signal Function Class Forward Channel Physical Layer Parameters

409

### 410 4.2.1.2 Power Function Class Forward Channel Physical Layer – Master Perspective

411 The  $V_{HIGH-PWR}$  and  $V_{LOW-PWR}$  voltages are required for all operational modes of the Power Function Class. The  $V_{IDLE}$ 412 voltage is required for the power phase.

The  $V_{\text{HIGH-PWR}}$  and  $V_{\text{LOW-PWR}}$  voltages are used for communication only.  $V_{\text{HIGH-PWR}}$  and  $V_{\text{LOW-PWR}}$  are fixed voltages as specified in Table 4-3.

415 The slave load current comes from a reservoir capacitor (H<sub>CAP</sub>) during the command and response phase of the

416 communication cycle. The H<sub>CAP</sub> is re-supplied during the power phase of the communication cycle. Current for the

417 Power Function Class loads is supplied from the master during the power phase. The flow of current between the

418 master and the H<sub>CAP</sub> is controlled with a power extraction diode or by synchronous rectification with an active switch.

The total bus load consists of static and dynamic loads. The static loads are the slave guiescent currents and any

420 additional loads that do not vary significantly during the response phase. The dynamic loads consist of the response

421 currents, the currents to recharge the  $H_{CAP}$  and the bus currents required to charge and discharge the harness and load

422 capacitors used for bus filtering and stabilization.

| Item | Characteristic / Symbol                                 | Condition / Notes                                                              | Min                                                                                                             | Тур | Max              | Unit |

|------|---------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|------------------|------|

| 13.  | V <sub>IDLE</sub>                                       | Power Phase Idle Voltage                                                       |                                                                                                                 |     | 25               | V    |

| 14.  | VIDLE Minus VHIGH-PWR                                   | Difference Between the Power Phase<br>Idle Voltage and the Signal High Voltage | 1                                                                                                               |     |                  | v    |

| 15.  | V <sub>HIGH-PWR</sub>                                   | Power Function Class Signal High<br>Voltage                                    | 3.5                                                                                                             | 4   | 4.5              | V    |

| 16.  | V <sub>LOW-PWR</sub>                                    | Power Function Class Signal Low<br>Voltage                                     | 1.75                                                                                                            | 2   | 2.25             | V    |

| 17.  | R <sub>M</sub>                                          | Master Source Resistance                                                       |                                                                                                                 |     | 10               | Ω    |

| 18.  | V <sub>HIGH-PWR_p-p</sub> During Response Phase         | Measured at Master<br>Peak to Peak Response Current ≤27mA                      | -500                                                                                                            |     | 500              | mV   |

| 19.  | I <sub>CL_PWR_MAX</sub>                                 | Supply Voltage Current Limit,<br>Measured at Master                            | <u></u> (200)                                                                                                   |     | <b>1</b> 2 (400) | mA   |

| 20.  | $V_{\text{HIGH-PWR}}$ to $V_{\text{LOW-PWR}}$ Slew Time | $C_{\rm BUS}$ = 15nF, 90% to 10% of $V_{\rm DELTA}$                            | <b>1</b> 2 (333)                                                                                                |     | 1000             | ns   |

| 21.  | $V_{\text{LOW-PWR}}$ to $V_{\text{HIGH-PWR}}$ Slew Time | $C_{BUS} = 15 nF$ , 10% to 90% of $V_{DELTA}$                                  | <b>1</b> 2 (333)                                                                                                |     | 1000             | ns   |

| 22.  | $V_{\text{IDLE}}$ to $V_{\text{HIGH-PWR}}$ Slew Time    | $C_{\rm BUS}$ = 15nF, 90% to 10% of $V_{\rm IDLE}$ - $V_{\rm HIGH-PWR}$        | <b>‡</b> 2 (1000)                                                                                               |     | 8000             | ns   |

| 23.  | $V_{\text{HIGH-PWR}}$ to $V_{\text{IDLE}}$ Slew Time    | $C_{\rm BUS}$ = 15nF, 10% to 90% of $V_{\rm IDLE}$ - $V_{\rm HIGH-PWR}$        | <u></u> |     | 8000             | ns   |

423

#### Table 4-3: Power Function Class Forward Channel Physical Layer Parameters

#### 424 4.2.2 Forward Channel Physical Layer - Slave Perspective

The slave must track the average value of the  $V_{HIGH}$  voltage. From the average  $V_{HIGH}$  voltage the slave can determine the  $V_{LOW}$  voltage relative to the  $V_{HIGH}$  voltage.

427 The slave voltage regulation scheme must be designed to account for the  $V_{HIGH}$  and  $V_{LOW}$  voltage levels (line

regulation). For Power Function Class slaves the slave must also detect the  $V_{IDLE}$  voltage and isolate load currents from the communication response current during the response phase.

430 The slave quiescent current must remain stable during the response phase. For Signal Function Class slaves a series

431 voltage regulation scheme can ensure stable quiescent current draw. For Power Function Class slaves the energy

432 extraction scheme isolates the slave load current from the response current during response phase.

433

## 434 **4.2.3** Forward Communication Channel Data Bit Encoding

The master Manchester encodes forward channel data bits onto the bus as transitions between the  $V_{HIGH}$  and  $V_{LOW}$  bus voltages. For the Power Function Class, the transitions between the  $V_{IDLE}$  and the  $V_{HIGH PWR}$  voltages do not encode

437 any information.

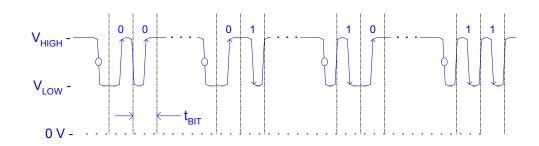

#### 438 **4.2.3.1** Forward Channel Data Bit Encoding - Master Perspective

439 For Command and Response Mode the master directly encodes forward channel data bits using a Manchester-1 format

440 where  $V_{\text{HIGH}}$  is considered the idle level and  $V_{\text{LOW}}$  is considered the signal level. Logic 1 bits are encoded as a 441 transition from  $V_{\text{HIGH}}$  to  $V_{\text{LOW}}$  whereas logic 0 bits are encoded as a transition from  $V_{\text{LOW}}$  to  $V_{\text{HIGH}}$  as shown in Figure

442 4-1.

443

#### 444

#### Figure 4-1: Forward Channel - Data Bit Encoding Examples

For Command and Response Mode all commands begin with a transition from the  $V_{HIGH}$  voltage to the  $V_{LOW}$  voltage levels and this transition occurs as defined within the temporal framework. The initial transition is followed by the

447 command bits as illustrated in Figure 4-1. The bit timing and tolerances are defined in Section 4.2.4.

448 For the Periodic Data Collection Mode the master sends a Broadcast Read Command. If the Background Diagnostic 449 Mode is used, the Broadcast Read Command is replaced by a predetermined number of Manchester encoded bits that

450 make up a complete diagnostic command over consecutive time periods. The number of diagnostic command bits sent

451 during each successive time period is based on the amount of reverse channel bandwidth allocated to the Background

452 Diagnostic Mode (reference Section 2.4.3).

453 The  $V_{HIGH}$  to  $V_{LOW}$  voltage levels for the forward channel are specified in Section 4.2.1. The timings parameters for the 454 forward channel are specified in Section 4.2.4.

#### 455 **4.2.3.2** Forward Channel Data Bit Decoding ~ Slave Perspective

The slave must detect the transition and transition polarity between the  $V_{HIGH}$  and  $V_{LOW}$  voltage levels. Polarity discrimination is used for command decoding and for clock synchronization.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 459 4.2.4 Forward Communication Channel Timing

460 Figure 4-2 shows the standard timing for a single Command and Response Mode transaction. For Command and

461 Response Mode there are defined time delays between the command phase and the response phase. For Power

462 Function Class, the master asserts the power phase following the command and response phase with an associated time

463 delay. Timings for the Command and Response Mode are relative to the initial transition from  $V_{HIGH}$  to  $V_{LOW}$  and are

464 preceded by a defined quiet time.

Section 4.5 introduces methods to take advantage of the protocol temporal framework to improve the system timing.

Implicit start bits are not required.

467

#### 468

#### Figure 4-2: Command and Response Mode Transaction

469 Figure 4-3 shows the standard timing for a single Periodic Data Collection Mode transaction. In the Periodic Data

470 Collection Mode the initial  $V_{HIGH}$  to  $V_{LOW}$  transition occurs at a pre-defined period as required by the application and 471 varified by the temperal framework. Implicit start bits are not required

471 verified by the temporal framework. Implicit start bits are not required.

472

473

#### Figure 4-3: Periodic Data Collection Mode Transaction

| Item | Characteristic / Symbol            | Condition / Notes          | Min             | Тур | Max            | Unit |

|------|------------------------------------|----------------------------|-----------------|-----|----------------|------|

| 24.  | t <sub>BIT_CRM</sub> (Figure 4-1)  | Command Bit Time in CRM    |                 | 8   |                | μs   |

| 25.  | t <sub>BIT_PDCM</sub> (Figure 4-1) | Command Bit Time in PDCM   |                 | 8   |                | μs   |

| 26.  | t <sub>BIT_BDM</sub> (Figure 4-1)  | Command Bit Time in BDM    |                 | 8   |                | μs   |

| 27.  | t <sub>BIT_TOL</sub>               | Command Bit Time Tolerance | <b>1</b> 6 (-1) |     | <b>1</b> 6 (1) | %    |

474

## Table 4-4: Forward Communication Timing Parameters

## 475 **4.3 Reverse Communication Channel Physical Layer**

The reverse communication physical layer is a current loop interface. There are three current levels defined for the reverse channel: the total quiescent current of all connected slaves ( $I_Q$ ), the 1x response level ( $I_{RESP}$ ) and the 2x response level ( $2*I_{RESP}$ ).

## 479 **4.3.1** Reverse Communication Channel Physical Layer - Slave Perspective

480

| Item | Characteristic / Symbol    | Condition / Notes                                                       | Min              | Тур | Max  | Unit |

|------|----------------------------|-------------------------------------------------------------------------|------------------|-----|------|------|

| 28.  | 2 * I <sub>RESP</sub>      | Second Level Response Current During Response Phase Not Including $I_Q$ | 21               | 24  | 27   | mA   |

| 29.  | I <sub>RESP</sub>          | First Level Response Current During Response Phase No Including $I_Q$   | 10.5             | 12  | 13.5 | mA   |

| 30.  | Response Current Slew Time | 10% to 90% of 2*I <sub>RESP</sub>                                       | <b>1</b> 4 (200) |     | 1000 | ns   |

481

#### Table 4-5: General Reverse Channel Physical Layer Slave Parameters

482 For Signal Function Class slaves, the reverse channel response signal assumes 3 distinct values:  $I_0$ ,  $I_0+I_{RESP}$  and

483  $I_0+2*I_{RESP}$ .  $I_0$  is the total quiescent current for all connected slaves.  $I_0$  must remain stable over periods of time

484 significantly longer than the message.

| Item | Characteristic / Symbol | Condition / Notes                                                                                  | Min | Тур | Max             | Unit |

|------|-------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----------------|------|

| 31.  | I <sub>Q</sub>          | Total Static Bus Loading                                                                           |     |     | <b>1</b> 2 (40) | mA   |

| 32.  | Iq_Slave                | Static Bus Loading per Slave                                                                       |     |     | <b>1</b> (10)   | mA   |

| 33.  | $\Delta I_Q$            | Change in Static Bus Loading Over Life                                                             | -5  |     | 5               | mA   |

| 34.  | d I <sub>Q</sub> /dt    | Total Static Bus Load Rate of Change<br>During Response Phase Excluding<br>Response Signal Current |     |     | 1               | mA/s |

485

#### Table 4-6: Signal Function Class Reverse Channel Physical Layer Slave Parameters

486 For Power Function Class slaves the reverse channel response signal assumes 3 distinct values:  $I_{Q_PWR}$ ,  $I_{Q_PWR}$ + $I_{RESP}$ 487 and  $I_{Q_PWR}$ +2\* $I_{RESP}$ . The load current and the response current are isolated from each other as described in Section

488

2.4.4.

| Item | Characteristic / Symbol | Condition / Notes                                                                                  | Min | Тур | Max            | Unit |

|------|-------------------------|----------------------------------------------------------------------------------------------------|-----|-----|----------------|------|

| 35.  | I <sub>LOAD_PWR</sub>   | Total Bus Load in Idle Phase                                                                       |     |     | <b>1</b> (100) | mA   |

| 36.  | I <sub>Q_PWR</sub>      | Total Static Bus Loading During<br>Communication Phase                                             |     |     | 1              | mA   |

| 37.  | d I <sub>Q</sub> /dt    | Total Static Bus Load Rate of Change<br>During Response Phase Excluding<br>Response Signal Current |     |     | 0.1            | mA/s |

489

#### Table 4-7: Power Function Class Reverse Channel Physical Layer Slave Parameters

#### 490 **4.3.2** Reverse Communication Channel Physical Layer - Master Perspective

The master interface must dynamically monitor the current supplied to the bus. In particular the master must sample the current supplied to the bus with sufficient resolution and sample rate to detect and discriminate between the 3 distinct currents. This detection and discrimination must assess both the magnitudes of the currents and the transitions between the various levels. Additionally the master must detect if the current is outside of the range appropriate for the class class on if the magnitude or transitions of the current is outside of the range appropriate for the detect of the current is outside of the range appropriate for the class class on if the magnitude or transitions of the range appropriate for the detect of the current is outside of the range appropriate for the

slave class or if the magnitudes or transitions violate specific timing and magnitude criteria.

#### 4.3.3 **Reverse Communication Channel Data Bit Encoding** 496

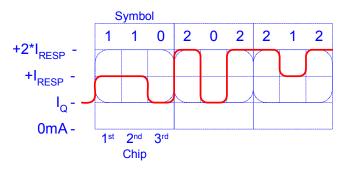

497 DSI3 uses multi-level source coded approach where data nibbles are first encoded into symbols and then the symbols

498 are encoded into current levels. Within a symbol there are 3 consecutive transmissions called *chips* that can assume

499 one of the three discrete current levels described in Section 4.3. Each symbol encodes the information of 4-bits. Figure 500

4-4 shows an example of a 3 symbol (9-chip) data packet (12 data bits).

501

#### 502

Figure 4-4: Response Data Bit Encoding - "Multi-Level Source Coded"

Of the 27 possible combinations for three consecutive tri-level chips, the combinations that begin with the null current 503 level  $(I_{\Omega})$  are discarded. Of the remaining 18 symbols, the two symbols that contain the same value for all three chips 504 are also discarded. The remaining 16 symbols all begin with a non-null current level and have at least one transition. 505

These characteristics guarantee that any response packet has a transition at the beginning of a packet and at least one 506

507 transition in every symbol. Table 4-8 specifies the symbol encoding used for DSI3 response transmissions.

| Encoded D | Symbol Transmitted |                      |                      |                      |

|-----------|--------------------|----------------------|----------------------|----------------------|

| Binary    | Hexadecimal        | 1 <sup>st</sup> Chip | 2 <sup>nd</sup> Chip | 3 <sup>rd</sup> Chip |

| 0000      | 0                  | 1                    | 1                    | 0                    |

| 0001      | 1                  | 2                    | 1                    | 1                    |

| 0010      | 2                  | 1                    | 0                    | 2                    |

| 0011      | 3                  | 2                    | 0                    | 2                    |

| 0100      | 4                  | 1                    | 0                    | 0                    |

| 0101      | 5                  | 2                    | 1                    | 2                    |

| 0110      | 6                  | 1                    | 1                    | 2                    |

| 0111      | 7                  | 2                    | 0                    | 1                    |

| 1000      | 8                  | 2                    | 2                    | 0                    |

| 1001      | 9                  | 2                    | 1                    | 0                    |

| 1010      | А                  | 1                    | 2                    | 2                    |

| 1011      | В                  | 2                    | 2                    | 1                    |

| 1100      | С                  | 1                    | 2                    | 0                    |

| 1101      | D                  | 2                    | 0                    | 0                    |

| 1110      | Е                  | 1                    | 0                    | 1                    |

| 1111      | F                  | 1                    | 2                    | 1                    |

#### 508

## Table 4-8: Symbol Mapping Example: Source ID 0x00

509 The reverse communication chip and symbol timing parameters are specified in Section 4.4. The timing parameters are

510 typically global for all response packets on a DSI3 network. However the specification only requires that the master and slave use the same chip timings. Slaves with different chip timings could exist on the same network if the master 511

512 has this capability.

#### 513 4.3.3.1 Reverse Communication Channel Data Bit Encoding - Slave Perspective

514 The slave encodes groups of 4 data bits into symbols. The chip timing for each specific slave and its master must

515 agree. The slave is responsible for encoding the timing information present in the symbols for recovery by the master.

516 The variations of chip times are actively controlled within the tolerances of the clock synchronization and management

scheme. Additional restrictions and requirements for slave response data encoding are specified in the data link layer

Section 5

#### 519 4.3.3.2 Reverse Communication Channel Data Bit Decoding - Master Perspective

520 The master and slave must agree on a common chip time. The master synchronizes symbol recovery with the initial

transition that begins every response packet. Slave response symbols have at least one guaranteed transition, allowing

the master to re-synchronizes as necessary during symbol recovery. The master must ensure that the response current levels are proper and that transitions between the specified levels occur at appropriate times. Finally each recovered

523 levels are proper and that transitions between the specified levels of 524 symbol must be one of the 16 possible symbols.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 526 **4.4 Reverse Communication Channel Timing Considerations**

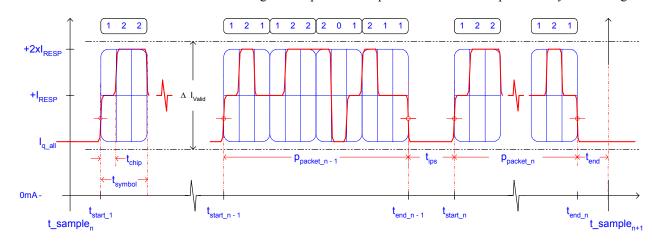

For the Periodic Data Collection Mode of the Signal Function Class multiple symbols are assembled into data packets and sent to the master as a TDMA frame. Figure 4-5 introduces the TDMA frame and some of the basic parameters associated with the frame. Each packet in the frame has a start time defined as a percentage of the sample period or in terms of real time. The time of the first packet is specified in terms of real time. The minimum or earliest time that the first packet can start allows sufficient time for a single bit command and the associated settling time. The first response packet in the TDMA frame may be further delayed based on the percentage of time reserved for Background Diagnostic Mode.

534 Section 4.5 introduces methods to take advantage of the protocol temporal framework to improve the system timing.

Figure 4-5: Multi-Level Source Coded TDMA Response Frame

537

| Item | Characteristic / Symbol       | Condition / Notes                      | Min               | Тур           | Max               | Unit  |

|------|-------------------------------|----------------------------------------|-------------------|---------------|-------------------|-------|

| 38.  | t <sub>chip</sub> Valid Range | Range of Valid Chip Times              | <b>1</b> 4 (2.70) |               | <b>1</b> 4 (10.0) | μs    |

| 39.  | t <sub>chip</sub> Tolerance   | Slave Chip Time Tolerance              | -5.0              |               | 5.0               | %     |

| 40.  | t <sub>symbol</sub>           | Symbol Time                            |                   | $3* t_{chip}$ |                   | μs    |

| 41.  | $t_{r\_start} - t_{c\_start}$ | Response Start Time, CRM (Figure 4-2)  | 280               | 295           | 310               | μs    |

| 42.  | $t_{start_l} - t_{c\_start}$  | Response Start time, PDCM (Figure 4-3) | 15                |               |                   | μs    |

| 43.  | t <sub>IPS</sub>              | Inter-Packet Separation (Figure 3-5)   | 1                 |               |                   | Chips |

| 44.  | t <sub>END</sub>              | Quiet Time Before Next Sample Period   | <b>1</b> € (10)   |               |                   | μs    |

Table 4-9 : Reverse Communication Channel Timing Parameters

539

## 540 **4.5 System Timing Considerations**

541 DSI3 defines a temporal framework and provides services for clock management and clock synchronization. The

temporal framework enables the system to perform timing checks based on a common expectation of when events

should occur within the system. The temporal framework allows the system to validate changes of state including the

544 ordering of events within the changes of state. With the temporal framework all devices on a bus develop a common 545 sense of time. Clock management and clock synchronization can be used to improve the efficiency of the system.

546 Commands define a *base period* for Periodic Data Collection Mode and perform basic clock synchronization. The

- 547 temporal framework provides error checks and validates the expected timing of the synchronization events.

- 548 The master node transmits commands at P<sub>SYS</sub> period from a stable time base of sufficient accuracy. The accuracy of the

- system generated synchronization period  $\Delta P_{SYS}$  is inherited by the master  $\Delta P_{Master}$  and then by the slave node  $\Delta P_{Slave}$ .

- 550 The system period variation  $\Delta P_{SYS}$  limits the overall accuracy of the system.

551 Clock management at slave nodes is based on the number of local oscillator cycles counted between commands. The

slave can also actively manage the local oscillator period to maintain the number of local oscillator cycles between

commands constant. Finally all of the timings in Periodic Data Collection Mode can be defined as fractional units ofthe base period.

Table 4-10 shows an example set of system parameters using the temporal framework to improve system timing. These

556 parameters are not required by the standard, but are only included as an example to show the potential of the temporal framework to improve system timing.

| Item | Characteristic / Symbol          | Condition / Notes                                                              | Min  | Тур | Max  | Unit                  |

|------|----------------------------------|--------------------------------------------------------------------------------|------|-----|------|-----------------------|

| 45.  | P <sub>SYS</sub>                 | Range of Valid PDCM Periods,<br>Example, not an Absolute Specification         | 100  |     | 5000 | μs                    |

| 46.  | $\Delta P_{SYS}$                 | PDCM Period Tolerance at the Master,<br>Example, not an Absolute Specification |      |     | 200  | ppm                   |

| 47.  | $\Delta P_{Master}$              | Master PDCM Period Tolerance,<br>Example, not an Absolute Specification        | -0.1 |     | 0.1  | %P <sub>SYS</sub>     |

| 48.  | $\Delta P_{Slave}$               | Measured PDCM Period at the Slave,<br>Example, not an Absolute Specification   | -0.7 |     | 0.7  | %P <sub>Master</sub>  |

| 49.  | $\Delta f_{Osc\_Slave\_Trained}$ | Trained Slave Oscillator Tolerance,<br>Example, not an Absolute Specification  | -0.5 |     | 0.5  | %                     |

| 50.  | $\Delta t_{Period}$              | PDCM Sample Period Jitter,<br>Example, not an Absolute Specification           | -0.1 |     | 0.1  | % P <sub>Master</sub> |

558

Table 4-10:

Example of DSI3 Timing Parameters Utilizing the Temporal Framework

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 560 **4.6 Number of DSI Buses and Nodes**

A DSI3 bus consists of single master and one or more slaves. The terms "network" and "bus" are used interchangeably with additional specificity concerning topology and class. DSI3 defines no maximum limit to the number of busses (networks) allowed in a system.

The maximum number of nodes on a DSI bus is 16 (1 master and 15 slaves). The minimum number is 2 (1 master and 1 slave). Each Signal Function Class slave supplies one or more data sources. Each Power Function Class slave supplies one or more power outputs and signal sources required for the intended function.

## 567 **4.7** Class-Mix and Mode Restrictions and Number of Nodes

568 Signal Function Class slaves can operate on the same bus with Power Function Class slaves provided that the master

accounts for the quiescent current of the Signal Function Class slaves. Also the Signal Function Class slave must

tolerate the idle voltage of the Power Function Class. Power Function Class slaves cannot exist on a Signal Function

571 Class bus since there is no power phase.

572 Signal Function Class and Power Function Class slaves both support the Command and Response Mode. The Signal 573 Function Class also supports the Periodic Data Collection Mode and, optionally, the Background Diagnostic Mode.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

574

# 5 DSI3 Data Link Layer

## 575 **5.1 Introduction**

The general philosophy of the DSI-3 data link layer follows earlier versions of the DSI specification in the sense that there is sufficient flexibility to tailor the protocol to satisfy the needs of diverse applications. This section is concerned primarily with the three fundamental modes of operation for the Signal Function Class: the Command and Response Mode, the Periodic Data Collection Mode and the Background Diagnostic Mode, as well as the Command and Response Mode for the Power Function Class.

581 For the Command and Response Mode a single command packet is followed by at most one response packet (There is 582 no response packet for a global command).

For the Periodic Data Collection Mode a command packet is followed by multiple response packets separated by interpacket separation times following a TDMA philosophy. The command packets for the Periodic Data Collection Mode are strictly periodic. The DSI3 standard does not limit the maximum number of response packets or the lengths of the response packets for Periodic Data Collection Mode. The master implementation imposes the practical limits on the maximum number and lengths of the response packets. The Periodic Data Collection Mode response packet start positions and lengths must be configured before entering Periodic Data Collection Mode. A preconfigured system can transition into Periodic Data Collection Mode immediately after applying power to the bus.

## 590 **5.1.1 Command Message Bit Order**

591 Most significant bits/bytes are transmitted before least significant bits/bytes. This ordering applies to both the message 592 bits and the CRC bits. Messages bits are transmitted before the CRC bits. This ordering allows for in-line CRC serial 593 calculations that terminate in an all zero value for successful transfers.

## 594 **5.1.2 Response Message Bit Order**

595 Most significant bits/bytes are transmitted before least significant bits/bytes. This ordering applies to both the message 596 bits and the CRC bits. Messages bits are transmitted before the CRC bits. This ordering allows for in-line CRC serial

calculations that terminate in an all zero value for successful transfers.

Implementation of the Bus Standard is governed by the terms of Section 1.3 of this document. Changes to this specification must be agreed to by DENSO CORPORATION, FREESCALE SEMICONDUCTOR INC. and TRW AUTOMOTIVE INC.

## 599 **5.2 Signal Function Class**

## 600 **5.2.1 Command and Response Mode Packet Formats**

601 Command and Response Mode data packets are exchanged primarily between a single master and a single slave. The 602 one exception to this is the use a global command which can be transmitted from one master to multiple slaves but 603 includes no slave response. The primary purpose of the command and response transactions are to read from and to 604 write to registers within the slave memory. Command and Response Mode utilizes a memory mapped access 605 philosophy to interface with slave registers. By changing the contents of slave data registers the application can read, 606 write or verify configuration of the slave and effect changes of state within the slave. The command, address and data 607 based interface used in previous versions of the protocol are also available. The system implementer may choose 608 between the memory mapped register access method and the command, address and data method. However the 609 memory mapped method provides greater flexibility.

610 The command and response structure provides all of the context information required for unambiguous single-exchange

611 transactions for extended memory applications requiring safety critical and efficient memory access. The structures 612 have pre-defined fixed bit timings for both the command and response packets. The transactions for the Signal

612 nave pre-defined fixed bit timings for both the command and response packets. The transactions for the Signal

Function Class are intended to be periodic and this feature may be used for initial clock training and temporal frame

work initialization as described in Section 4.5. The standard defines a set of fields that constitute the command and

response message structure. The details of the command formats can be preprogrammed within the implementation or

616 configured at run-time.

617 The Command and Response Mode command format is shown in Table 5-1.

| MSB              |          |               |               |          |  |  |

|------------------|----------|---------------|---------------|----------|--|--|

| Physical Address | Command  | Extended Data | Register Data | CRC      |  |  |

| PA[3:0]          | CMD[3:0] | ED[7:0]       | RD[7:0]       | CRC[7:0] |  |  |

618

#### Table 5-1: Command and Response Mode - Command Format

#### The Command and Response Mode response format is shown in Table 5-2.

| MSB              |        |               |               |          |  |  |

|------------------|--------|---------------|---------------|----------|--|--|

| Physical Address | Status | Extended Data | Register Data | CRC      |  |  |

| PA[3:0]          | S[3:0] | ED[7:0]       | RD[7:0]       | CRC[7:0] |  |  |

#### 620

## Table 5-2: Command and Response Mode - Response Format

621 The field definitions are shown in Table 5-3.

| Field    | Command Packet   | Length<br>(Bits) | Field    | Response Packet  | Length<br>(Bits) |

|----------|------------------|------------------|----------|------------------|------------------|

| PA[3:0]  | Physical Address | 4                | PA[3:0]  | Physical Address | 4                |

| CMD[3:0] | Command          | 4                | S[3:0]   | Status           | 4                |

| ED[7:0]  | Extended Data    | 8                | ED[7:0]  | Extended Data    | 8                |

| RD[7:0]  | Register Data    | 8                | RD[7:0]  | Register Data    | 8                |

| CRC[7:0] |                  | 8                | CRC[7:0] |                  | 8                |

622 623

#### Table 5-3: Command and Response Mode - Field Definitions

| 624 | The Command and Respons | e Mode supports the commands listed in Table 5-4: |

|-----|-------------------------|---------------------------------------------------|

|     |                         |                                                   |

| Command | Command Description      | Extended Data ED[7:0]    |

|---------|--------------------------|--------------------------|

| 0       | Register Read            | Register Address RA[7:0] |

| 2-7     | Device / System Specific | Device / System Specific |

| 8       | Register Write           | Register Address RA[7:0] |

| 9 - 15  | Device / System Specific | Device / System Specific |

#### 625

### Table 5-4: Command and Response Mode - Supported Commands

The Signal Function Class Command and Response Mode response status is defined in Table 5-5, with an example implementation:

| Commands 0 and 8                      |                         |                       |                                      |  |  |  |

|---------------------------------------|-------------------------|-----------------------|--------------------------------------|--|--|--|

| S[3]                                  | S[2:0]                  | Standard Description  | Device Description (Example)         |  |  |  |